ECE 428 Programmable ASIC Design

# Fundamentals of Digital IC Design

Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901

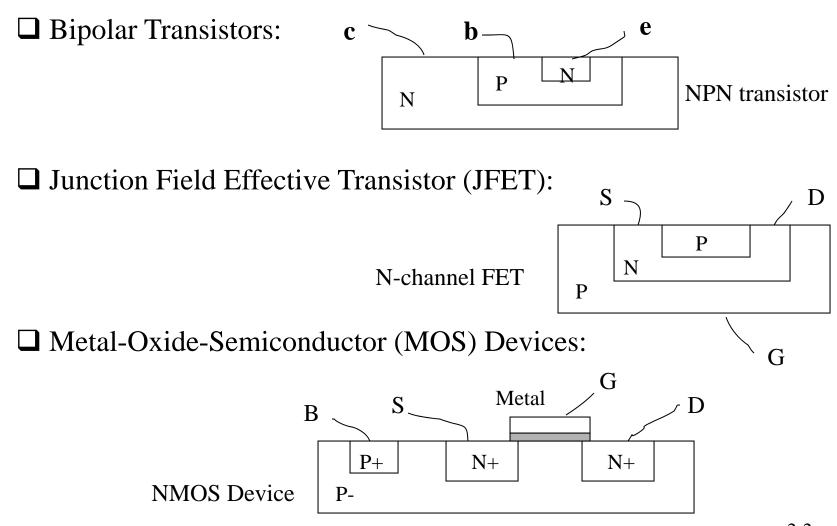

### **Semiconductor Devices**

2-2

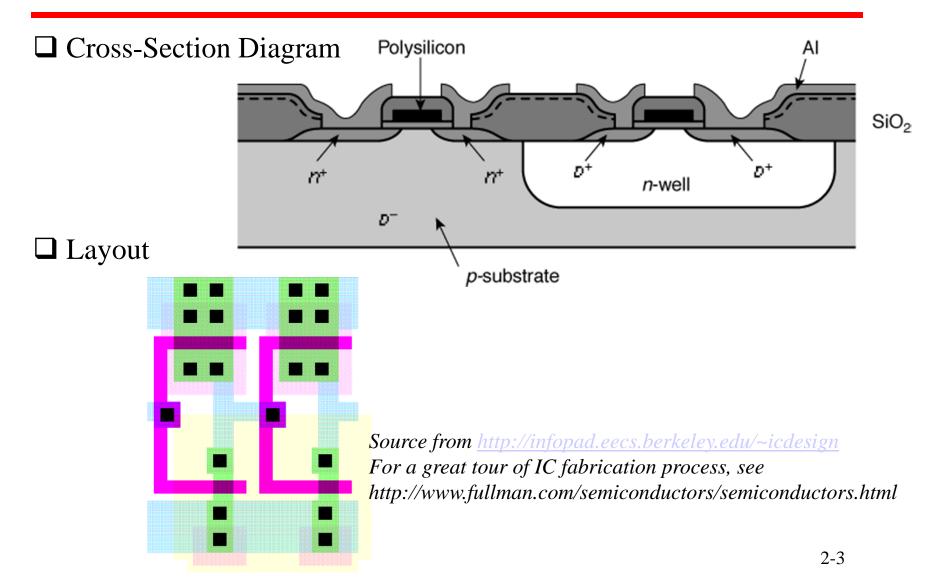

### **CMOS** Process

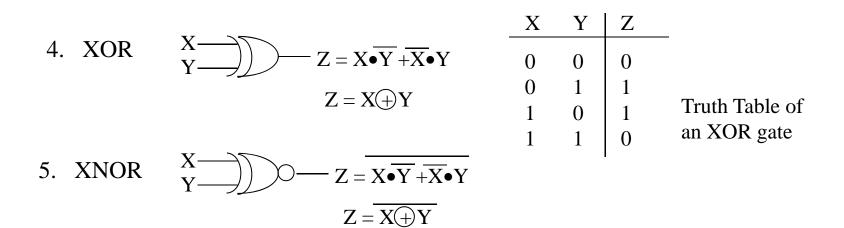

### Digital Signals and Basic Logic Gates

#### Digital signal values High Voltage (e.g. 5V)<sub>12</sub> True 1 Low Voltage (e.g. 0V) False 0 □ Basic logic gates Х Y 1. Inverter Х- $-Y = \overline{X}$ Truth Table of 1 0 0 an inverter 1 Ζ Х Y X-2. AND $Z = X \bullet Y$ 0 0 0 Y-1 0 0 Truth Table of 0 1 0 an AND gate 1 1 1 X 3. NAND $Z = X \bullet Y$ Y

### Basic Logic Gates

|        |                               | Х | Y | Ζ |                |

|--------|-------------------------------|---|---|---|----------------|

| 4. OR  | $X \longrightarrow Z = X + Y$ | 0 | 0 | 0 | _              |

|        |                               | 0 | 1 | 1 |                |

|        |                               | 1 | 0 | 1 | Truth Table of |

|        |                               | 1 | 1 | 1 | an OR gate     |

| 5. NOR | $X \longrightarrow Z = X + Y$ |   |   | I |                |

2-5

### Basic Logic Gates

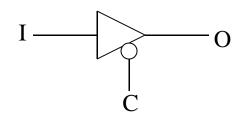

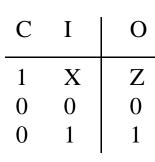

□ Tri-state Buffer

Truth table of a tri-state buffer

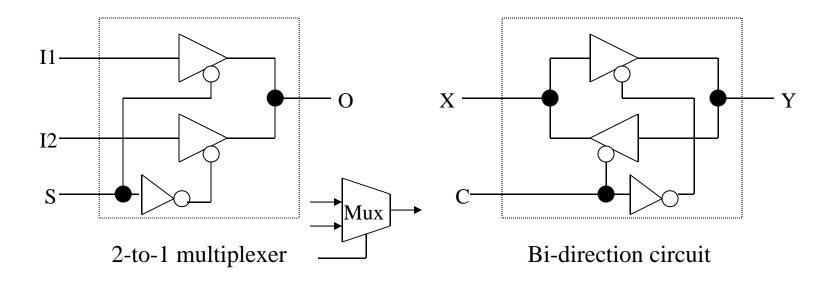

### Gate Delay Definition

2-7

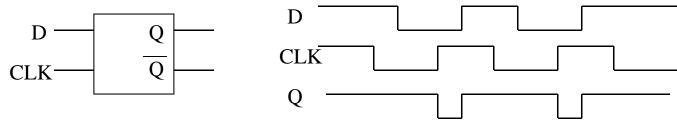

D latch

➢ When CLK=1, Q always reflects the signal value at input D

➤ If CLK=0, Q stores the last D value which appears at D just before CLK falls to 0

D Flip-flop

- D flip-flop will not change its output values unless there is a negative edge event at CLK input (CLK switches from logic 1 to 0).

- > When a negative edge appears at CLK input, D Flip-flop updates Q to the current D value

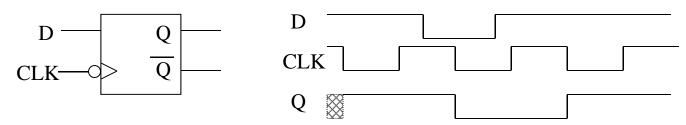

### Timing Parameters for D Flip-Flops

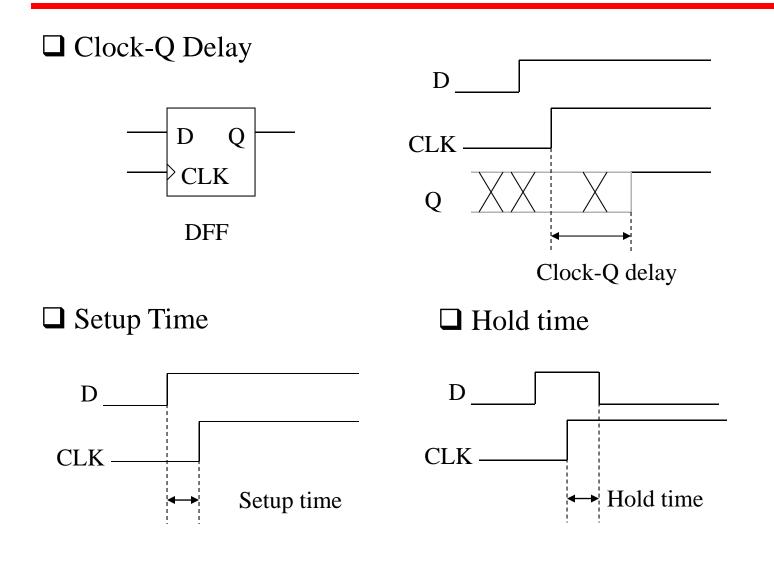

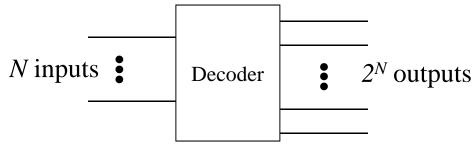

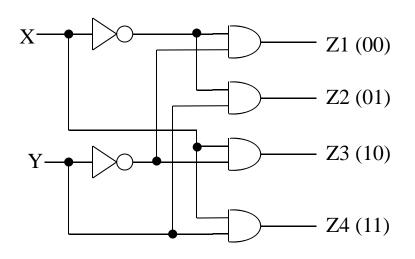

### **Decoder Circuits**

A decoder circuit uniquely selects one of its outputs according to its input signals

□ 2-to-4 decoder implementation

| X Y                                                               | Z1 | Z2 | Z3 | Z4 |

|-------------------------------------------------------------------|----|----|----|----|

| $\begin{array}{ccc} 0 & 0 \\ 0 & 1 \\ 1 & 0 \\ 1 & 1 \end{array}$ | 1  | 0  | 0  | 0  |

|                                                                   | 0  | 1  | 0  | 0  |

|                                                                   | 0  | 0  | 1  | 0  |

|                                                                   | 0  | 0  | 0  | 1  |

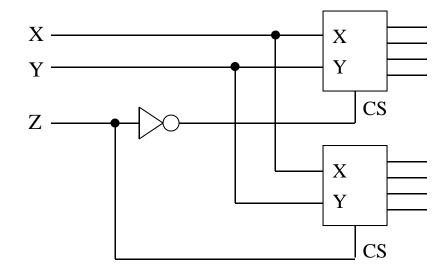

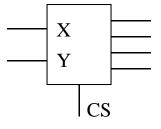

### Decoder Circuit

#### □ 3-to-8 decoder implementation

- ≻ Assume that we have 2-to-4 decoders available as standard components

- ➤ When CS is low (0), all the outputs of the decoder are low (0)

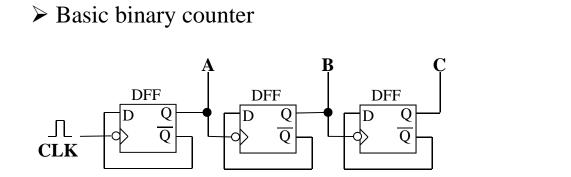

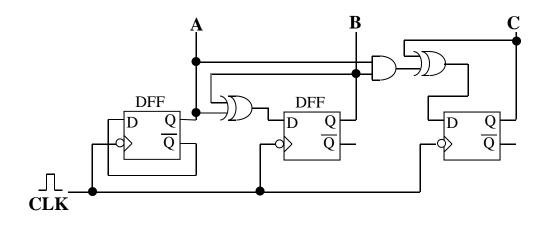

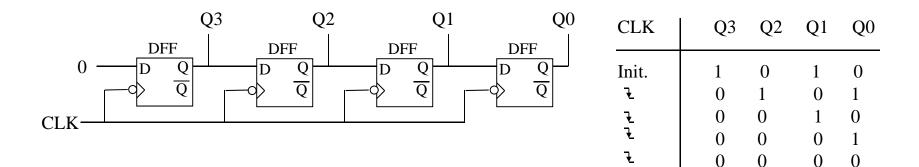

Counter

Synchronous counter

| Clk   | С | В | A |

|-------|---|---|---|

| Lu:4  | 0 | 0 | 0 |

| Init. | 0 | 0 | 0 |

| Ł     | 0 | 0 | 1 |

| Ł     | 0 | 1 | 0 |

| Ł     | 0 | 1 | 1 |

| Ł     | 1 | 0 | 0 |

| Ł     | 1 | 0 | 1 |

| Ł     | 1 | 1 | 0 |

| ٦.    | 1 | 1 | 1 |

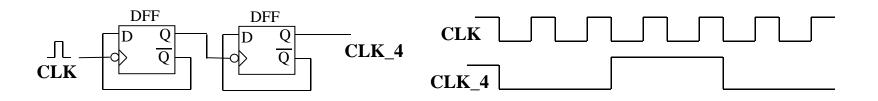

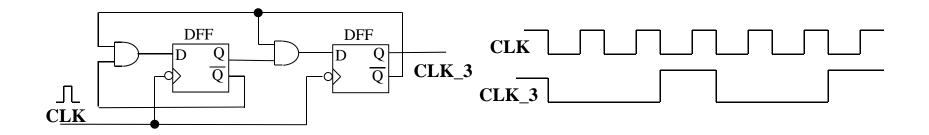

□ frequency divider

Divide clock frequency by 4

Divide clock frequency by 3

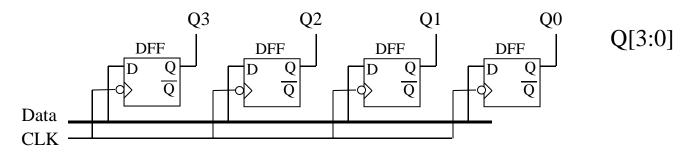

**Register**

A row of storage elements (e.g. D flip-flops)

□ Shift register

2-14

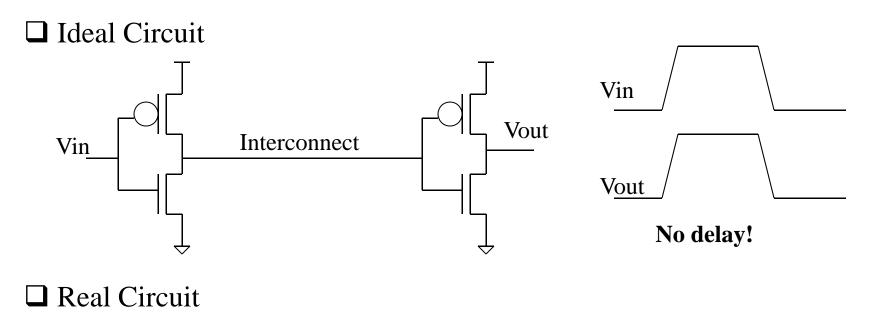

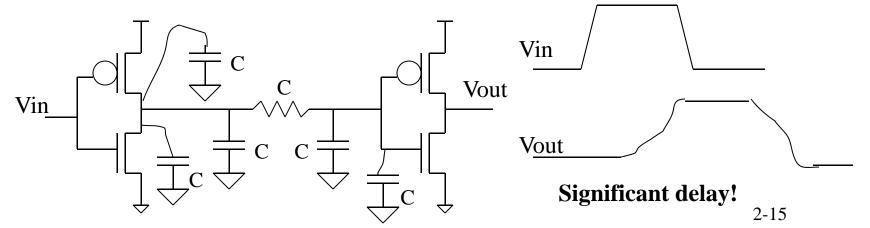

### Major Parasitic Effects in Digital ICs

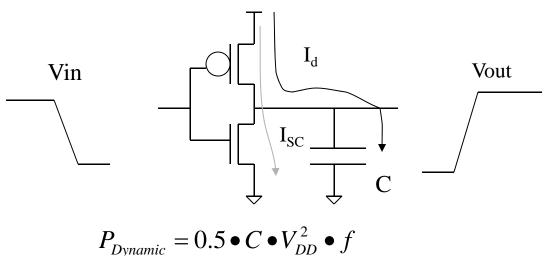

### Power Consumption of CMOS Gates

#### Dynamic Power Consumption

□ Short-Circuit Power Consumption

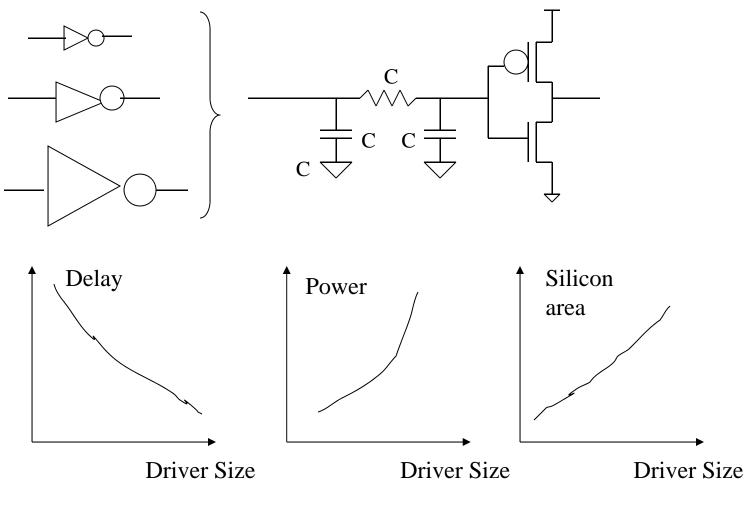

### **Transistor Sizing**

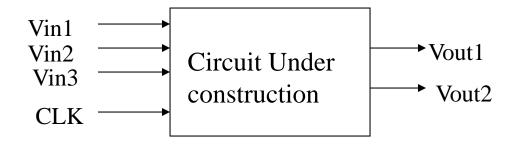

### Design Constraints for Digital ICs

Delay (speed) constraints

For example, the delay from Vin1 to Vout1 should be smaller than 10 ns; the clock frequency should be greater 100MHz

#### Power constraints

□ Area constraints

# How to Find Circuits Complying with Design Constraints

| Full-custom approach                                                                                                                                                                                                             | Standard-cell based approach<br>Gate-array approach<br>FPGA approach                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>It heavily depends on<br/>designers' expertise.</li> <li>Finding a proper circuit<br/>implementation can be<br/>very time consuming.</li> <li>Very creative circuit<br/>implementations can be<br/>achieved.</li> </ol> | <ol> <li>These approaches heavily use<br/>design automation techniques<br/>to search circuits complying with<br/>constraints.</li> <li>They are time saving approaches.</li> <li>These approaches require<br/>pre-developed technology libraries.</li> <li>The quality of the final implementa<br/>depends on algorithms and libraries<br/>used in the search.</li> </ol> |

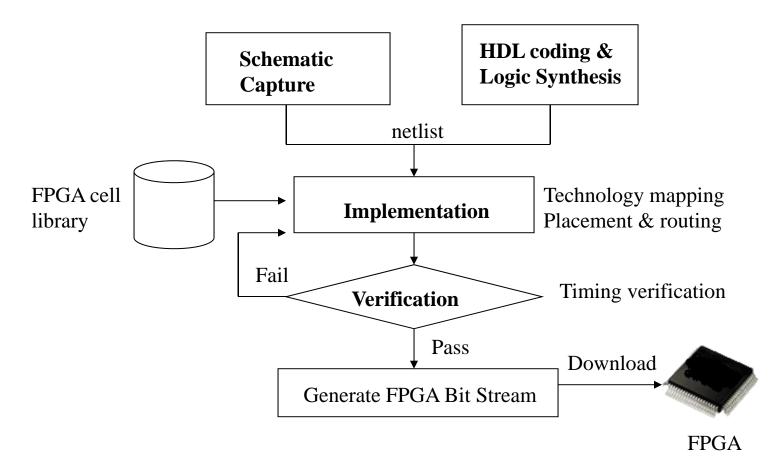

### □ FPGA Design Flow

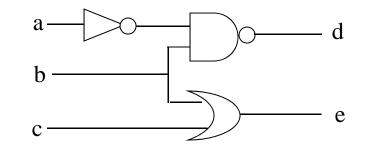

### Given Logic Function

This circuit is either from schematic capture or from logic synthesis

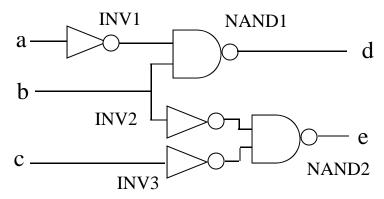

#### □ FPGA Library Components

- The library contains five components

- Three inverters at size 1, 3, 5

- Two two-input NAND gates at size 1 and 3

#### Design Constraints

— The maximum delay between an input and an output should not exceed 5 ns

Step 1: Use the available logic gates to implement the given function. (Technology Mapping)

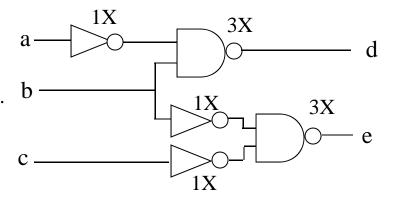

□ Step 2: Select proper size for each gate used in the above circuit.

(Gate Sizing)

- After this step, the circuit can be simulated to verify that it complies with timing constraints.

- In the simulation, the parasitic capacitance and resistance on interconnects are estimated (Estimated wire load)

2 - 22

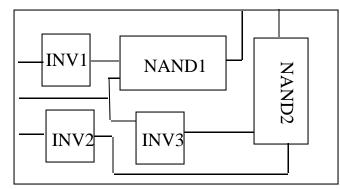

□ Step 3: Determine where to place these gates and how to connect them (Placement & Routing).

- Some algorithms first place the components and then route the interconnects.

- Some algorithms perform the placement and routing simultaneously

Steps 1, 2, and 3 are included in the implementation phase of the FPGA design Flow

□ Step 4: Perform post-layout simulation to verify that the generated circuit complies with timing constraints

- Since detail information of each interconnect is available, the circuit can be simulated with accurate wire load.

- The process that writes the accurate wire load into the circuit netlist is called back annotation

# What Information Should Be Stored in FPGA Library

- □ Logic function

- □ Timing (delay) information

- □ Power consumption information

- □ Silicon area

- □ Layout information

- □ Placement & routing constraints

- . ....

### Example: How to Store Delay Information

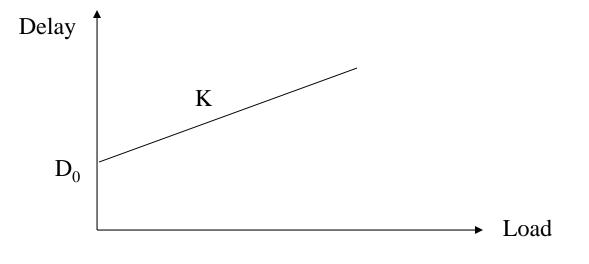

□ Normally, the delay of gate is proportional to the load on its output

$Delay = D_0 + K*Load$

So, we can store two parameters ( $D_0$  and K) for each gate to model its delay property.

### Binary Number System

Converting binary numbers to decimal numbers

Binary Decimal 1011  $\rightarrow$  1\*2^3 + 0\*2^2 + 1\*2^1 + 1\*2^0 = 11 0111  $\rightarrow$  0\*2^3 + 1\*2^2 + 1\*2^1 + 1\*2^0 = 7

Converting binary numbers to hexadecimal numbers

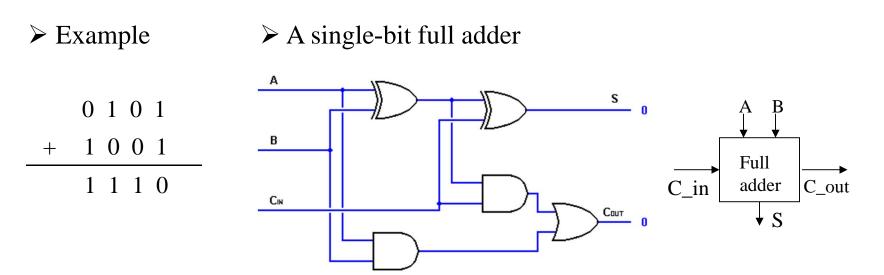

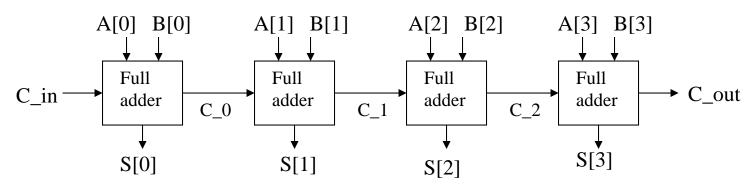

### **Binary Addition**

➤ 4-bit adder

## Handling Negative numbers

| □ Signed magnitude                                                                                                                                              |                | Signed magnitude                |                            |                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------|----------------------------|-----------------------------|--|

|                                                                                                                                                                 | 0              | 0                               | 0                          | 0                           |  |

| The left-most bit is a sign bit O indicates positive a number and                                                                                               | 0              | 0                               | 1                          | 1                           |  |

|                                                                                                                                                                 | 0              | 1                               | 0                          | 2                           |  |

| 0 indicates positive a number and                                                                                                                               | 0              | 1                               | 1                          | 3                           |  |

| 1 indicates negative a number                                                                                                                                   | 1              | 0                               | 0                          | 0                           |  |

|                                                                                                                                                                 | 1              | 0                               | 1                          | -1                          |  |

|                                                                                                                                                                 | 1              | 1                               | 0                          | -2                          |  |

|                                                                                                                                                                 | 1              | 1                               | 1                          | -3                          |  |

|                                                                                                                                                                 |                |                                 |                            |                             |  |

| • One's complement                                                                                                                                              | 1's complement |                                 |                            |                             |  |

| • One's complement                                                                                                                                              | 1's con        | plen                            | nent                       | Decimal                     |  |

| One's complement                                                                                                                                                | 1's com 0      | $\frac{1}{0}$                   | nent<br>0                  | Decimal 0                   |  |

|                                                                                                                                                                 |                | -                               |                            |                             |  |

| $\blacktriangleright$ For positive number A, it is                                                                                                              | 0              | 0                               | 0                          |                             |  |

|                                                                                                                                                                 | 0<br>0         | 0 0                             | 0<br>1                     | 0<br>1                      |  |

| For positive number A, it is represented as usual binary number                                                                                                 | 0<br>0<br>0    | 0<br>0<br>1                     | 0<br>1<br>0                | 0<br>1<br>2                 |  |

| <ul> <li>For positive number A, it is represented as usual binary number</li> <li>For negative number -A, its</li> </ul>                                        | 0<br>0<br>0    | 0<br>0<br>1<br>1                | 0<br>1<br>0<br>1           | 0<br>1<br>2<br>3            |  |

| <ul> <li>For positive number A, it is represented as usual binary number</li> <li>For negative number -A, its representation is obtained by flipping</li> </ul> | 0<br>0<br>0    | 0<br>0<br>1<br>1<br>1           | 0<br>1<br>0<br>1<br>1      | 0<br>1<br>2<br>3<br>0       |  |

| <ul> <li>For positive number A, it is represented as usual binary number</li> <li>For negative number -A, its</li> </ul>                                        | 0<br>0<br>0    | 0<br>0<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>0<br>1<br>1<br>0 | 0<br>1<br>2<br>3<br>0<br>-1 |  |

### Handling Negative numbers

| Two's complement                                                            | 2's complement |   |   | Decimal |

|-----------------------------------------------------------------------------|----------------|---|---|---------|

|                                                                             | 0              | 0 | 0 | 0       |

| $\succ$ For positive number A, it is the                                    | 0              | 0 | 1 | 1       |

| same as the one's complement                                                | 0              | 1 | 0 | 2       |

|                                                                             | 0              | 1 | 1 | 3       |

| For negative number A, add one<br>to the one's complement<br>representation | 1              | 1 | 1 | -1      |

|                                                                             | 1              | 1 | 0 | -2      |

|                                                                             | 1              | 0 | 1 | -3      |

| representation                                                              | 1              | 0 | 0 | -4      |

|                                                                             |                |   |   |         |

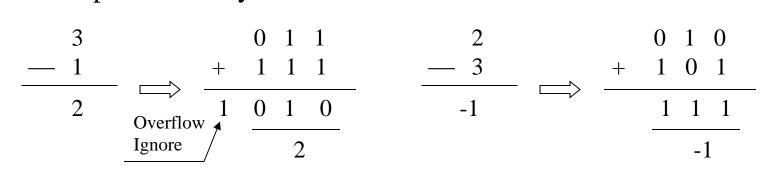

By using two's complement number representation, minus operations can be performed by adders