ECE 428 Programmable ASIC Design

# Issues in ASIC Design with Multi-Clock Domains

Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901

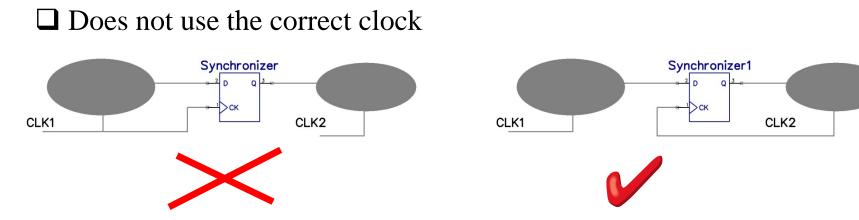

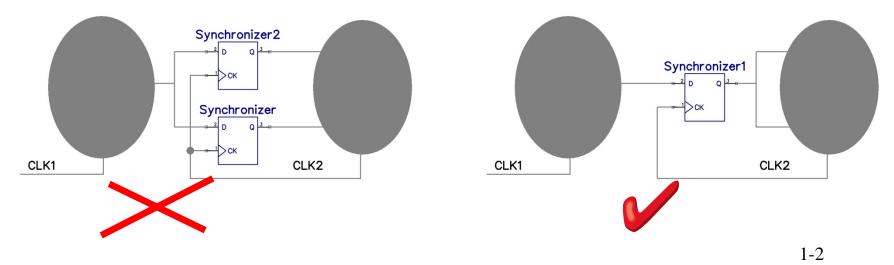

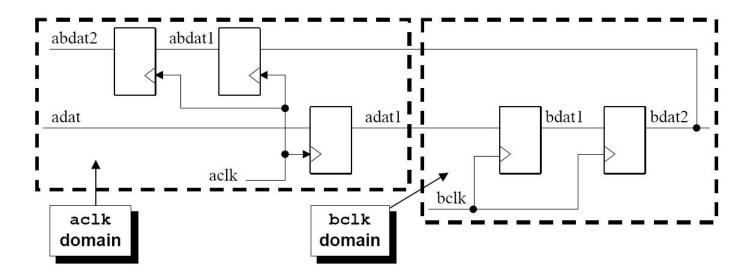

### Mistakes in the Use of Synchronizer

□ Synchronize the same signal more than once

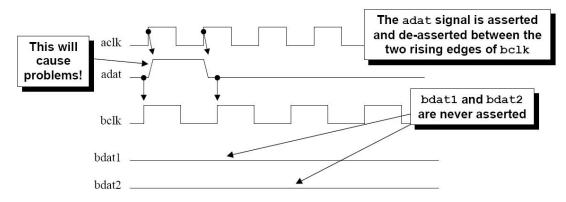

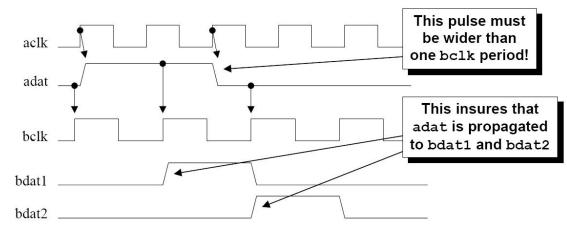

## Passing a control signal from slow clock domain to fast clock domain

$\Box$  The control signal may not be captured by the slow clock domain

Assert the control signal for a time period longer than the slow clock period

Source: Clifford Cummings, "Synthesis and Scripting Techniques for Designing Multi Asynchronous Clock Designs", 1-3

## Passing a control signal from slow clock domain to fast clock domain

□ Feedback the control signal as the acknowledge signal

- Don't have to consider the relation between clock periods

- ✤ Introduce significant delay due to the latency of the synchronizer

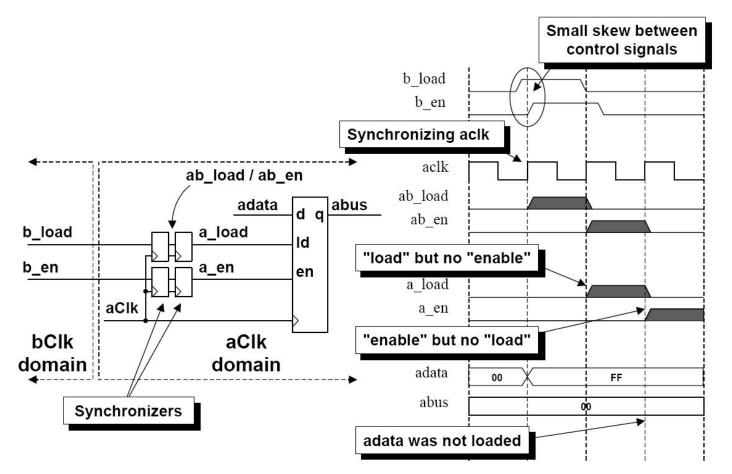

□ CASE 1: two simultaneously required control signal

Source: Clifford Cummings, "Synthesis and Scripting Techniques for Designing Multi Asynchronous Clock Designs", 1-5

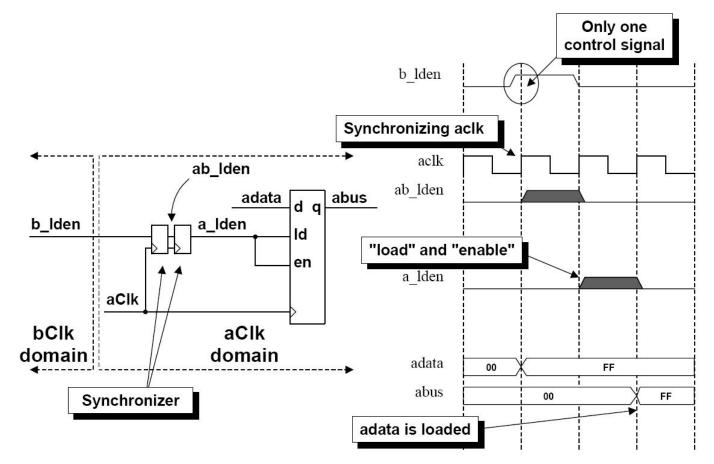

Derived the two control signal from a single signal

Source: Clifford Cummings, "Synthesis and Scripting Techniques for Designing Multi Asynchronous Clock Designs", <sup>1-6</sup>

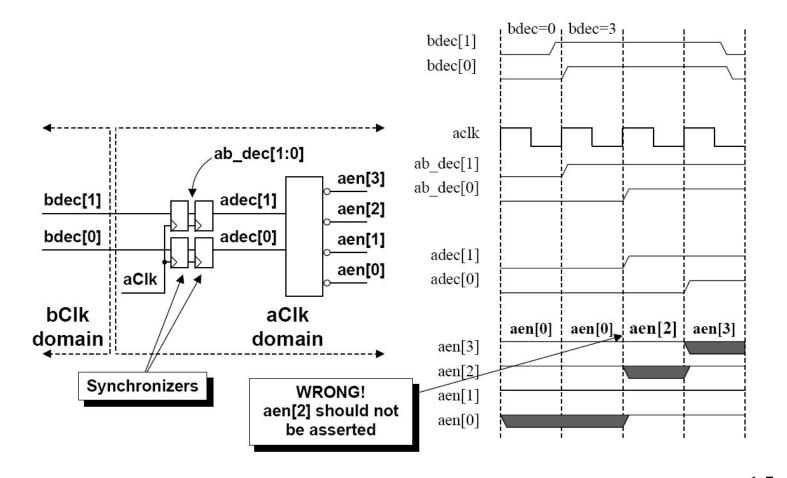

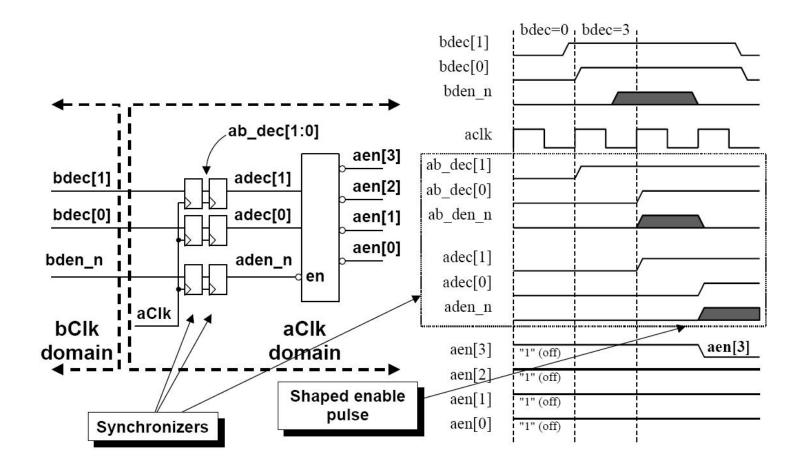

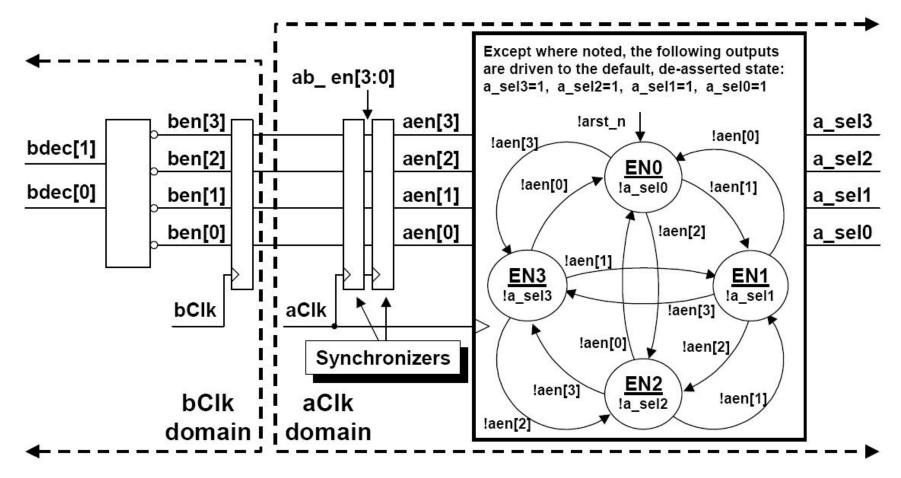

#### □ CASE 2: two encoded signals

Source: Clifford Cummings, "Synthesis and Scripting Techniques for Designing Multi Asynchronous Clock Designs", 1-7

□ Solution 1: added synchronized enable signal

Source: Clifford Cummings, "Synthesis and Scripting Techniques for Designing Multi Asynchronous Clock Designs", <sup>1-8</sup>

□ Solution 2:

Source: Clifford Cummings, "Synthesis and Scripting Techniques for Designing Multi Asynchronous Clock Designs", <sup>1-9</sup>

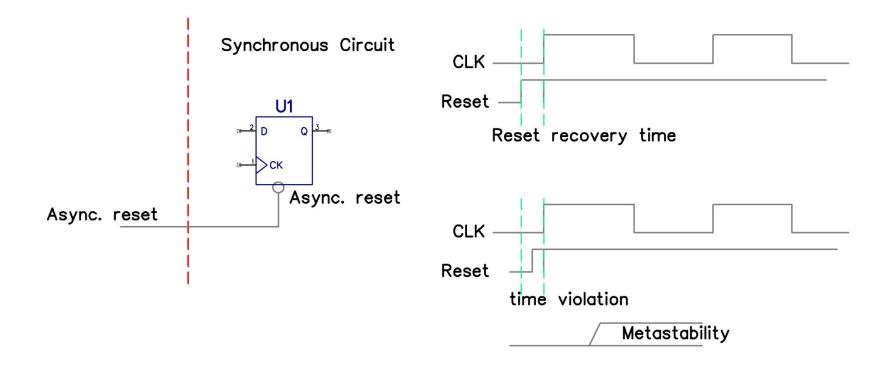

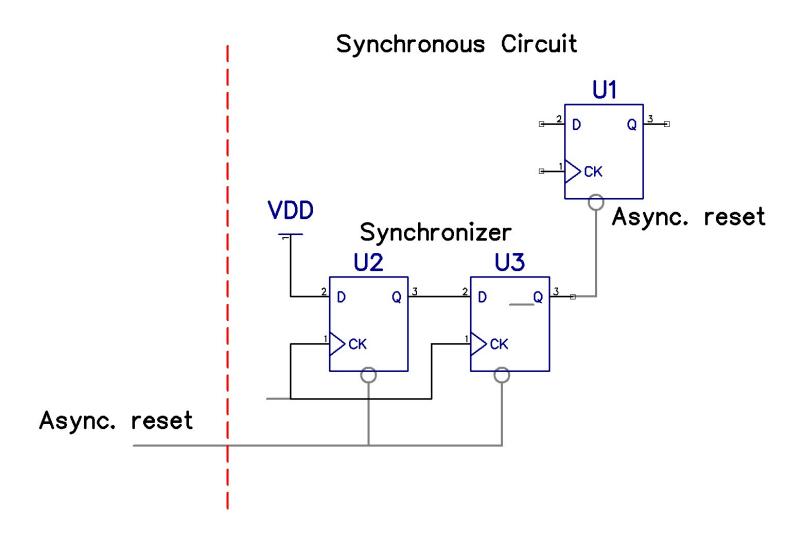

### Asynchronous Reset/Set

### Synchronous Reset/Set

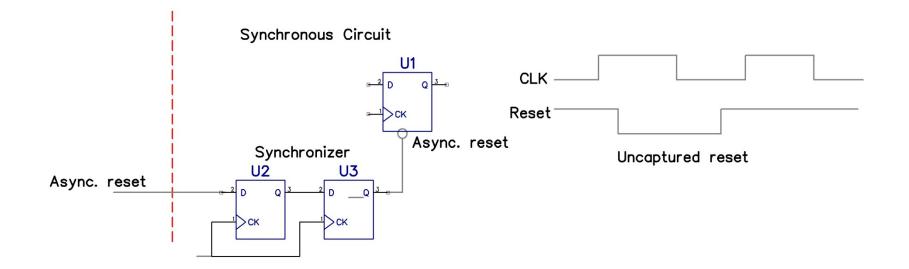

## Asynchronous Assertion and Synchronous Desertion Reset/Set

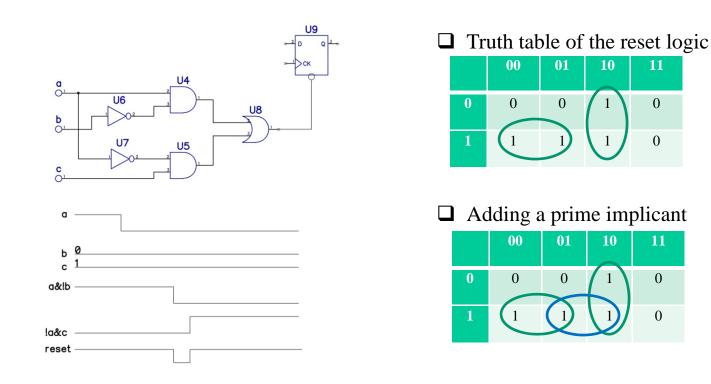

### Internally Generated Reset/Set

- □ It is preferred to use synchronous reset/set if the reset/set signal is internally generated

- □ If asynchronous reset/set has to be used, need make sure the circuit that generates the reset/set signal is glitch free.

Source: Steve Kilts, "Advanced FPGA Design"

0

0

11

0

0